What are the sizes of tword, oword and yword operands, as used in the NASM/YASM manual? And on a related note, is there a trick or underlying idea to these names? Is there a way by which bigger word sizes are given logical names?

I know that while word sizes may differ between systems, a NASM word is 2 bytes, dword is double that (4 bytes), qword is a quad word (8 bytes), but... is tword a triple word (6 bytes)? And for oword and yword I can't even think of a plausible meaning.

Note that it is probably an easy question, but I couldn't find an answer. In the NASM and YASM manuals these sizes are not explained, not even at the DQ, DT, DY, RESQ, REST, RESY pseudo-instructions. I read somewhere that MASM uses a similar system, but could not find anything on that either.

Edit: Based on the answers, this is the complete list:

- 1 byte (8 bit):

byte, DB, RESB

- 2 bytes (16 bit):

word, DW, RESW

- 4 bytes (32 bit):

dword, DD, RESD

- 8 bytes (64 bit):

qword, DQ, RESQ

- 10 bytes (80 bit):

tword, DT, REST

- 16 bytes (128 bit):

oword, DO, RESO, DDQ, RESDQ

- 32 bytes (256 bit):

yword, DY, RESY

- 64 bytes (512 bit):

zword, DZ, RESZ

Looking at TFS, it looks like:

- 'oword'/'DO' is 8 times as big as "word" (O for octoword), synonymous with dqword ("double-quad"); that would be 128 bits, corresponding to the size of an SSE vector register.

- 'tword'/'DT' is 80 bits (T for ten bytes), the full size of an Intel x87 floating point register.

- 'yword'/'DY' is 256 bits, and the Y is presumably mnemonic for the YMM names of the 256-bit vector registers in the Intel AVX extensions.

- 'zword'/'DZ' is 512 bits, Z for the ZMM names of the 512-bit vector registers in the Intel AVX-512 extensions.

So, not exactly a logical naming convention.

I have checked it with two approaches for NASM: source code and empirical.

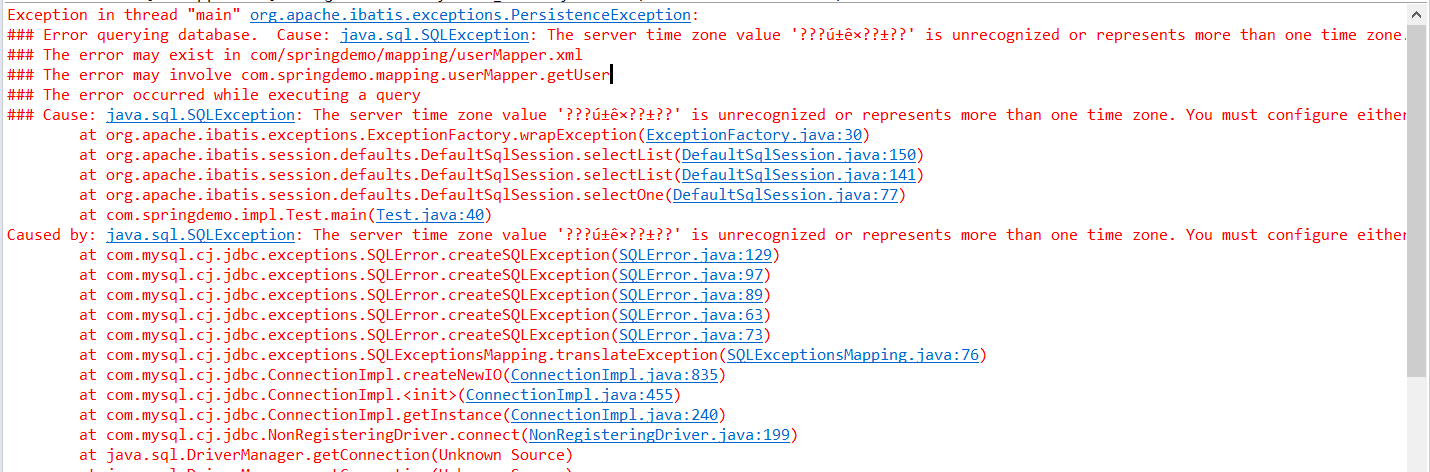

Source code

Source at: http://repo.or.cz/w/nasm.git

Then:

git grep -C2 tword

And we fall upon:

switch (size) {

case 1:

return "byte";

case 2:

return "word";

case 4:

return "dword";

case 8:

return "qword";

case 10:

return "tword";

case 16:

return "oword";

case 32:

return "yword";

case 64:

return "zword";

default:

return "???";

}

Empirical

git log -p and git tag --contains tell me that zword was added in 2.11, and since I'm on 2.10 and lazy, I'll omit that one.

On our .asm file:

section .bss

resb1 resb 1

resw1 resw 1

resq1 resq 1

rest1 rest 1

reso1 reso 1

resy1 resy 1

; Just to read the objdump better.

resb2 resb 1

Then compile and:

objdump -D -j .bss main.o

gives:

00000000 <resb1>:

...

00000001 <resw1>:

...

00000003 <resd1>:

3: 00 00 add %al,(%eax)

...

00000007 <resq1>:

...

0000000f <rest1>:

...

00000019 <reso1>:

...

00000029 <resy1>:

...

00000049 <resb2>:

...

If we take the differences between each position, we reach the same conclusion as before.

zword menemonic

For the ZMM registers added by AVX-512: https://en.wikipedia.org/wiki/AVX-512

I wonder what Intel will do when the letters of the alphabet end.