在Linux世界中,让纳米秒精密计时器/ clockticks不等人可以使用:

#include <sys/time.h>

int foo()

{

timespec ts;

clock_gettime(CLOCK_REALTIME, &ts);

//--snip--

}

这样的回答表明了asm方法来直接为CPU时钟与查询RDTSC指令。

在多芯,多处理器体系结构,该时钟是如何蜱/定时器值在多个内核/处理器同步? 我的理解是,在固有的击剑那里正在做。 这是理解是否正确?

你可以建议一些文件,将详细解释一下吗? 我感兴趣的英特尔Nehalem处理器与Sandy Bridge微架构的。

编辑

限制过程中的单核或CPU是不是一种选择,因为过程实在是巨大的(在资源消耗方面),并想以最佳方式利用所有资源,包括所有的内核和处理器的机器。

编辑

感谢您的TSC跨内核和处理器同步确认。 但我原来的问题是这是怎么做同步? 它是用某种围栏? 你知道任何公开的文件?

结论

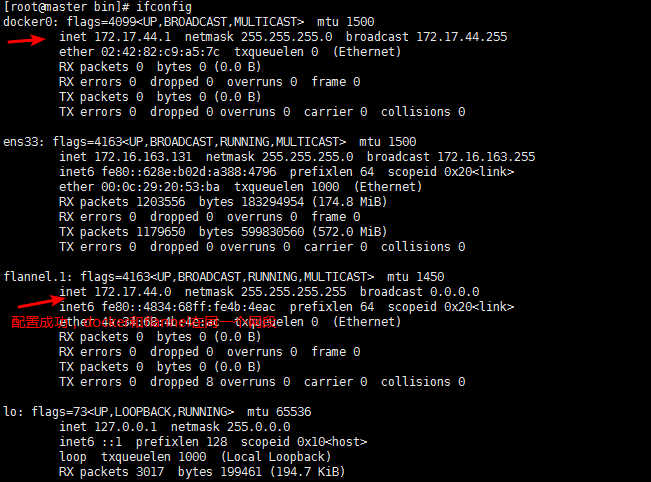

感谢所有的输入:这里的结论,这个讨论:TSC的正在使用的跨内核和处理器发生在多处理器/多核心系统复位在初始化同步。 而在这之后的每核心是对自己。 所述的TSC保持不变的锁相环一阶段,将归一给定的芯内的频率变化,因而时钟变化,那就是如何TSC保持在跨内核和处理器同步。

在较新的CPU(酷睿i7的Nehalem + IIRC)的TSC在所有核心synchronzied并运行一个恒定的速率。 因此,对于单个处理器,或单一套件或主板不止一个处理器(!),你可以依靠synchronzied TSC。

从英特尔系统手册16.12.1

在新的处理器时间戳计数器可以支持增强,简称不变TSC。 对于不变的TSC处理器的支持,通过CPUID.80000007H指示:EDX [8]。 不变TSC将在所有ACPI P-,C-恒定的速率运行。 和T状态。 这是建筑的行为前进。

在旧的处理器,你可以不依赖于任何恒定速率或synchronziation。

编辑:至少在多个处理器在单个封装或主板上的不变的TSC是同步的。 该TSC是复位以/复位到零,然后在每个处理器上的恒定速率蜱向前,没有漂移。 的/ RESET信号是保证在每个处理器在同一时间到达。

直接从英特尔,这里有一个如何近期处理器保持蜱以恒定速率TSC,是一个多功能插座主板上的核心和包间的同步的解释,甚至可能继续滴答当处理器进入深度睡眠C状态,特别是看到VIPIN库马尔EK(英特尔)的解释:

http://software.intel.com/en-us/articles/best-timing-function-for-measuring-ipp-api-timing/

下面是来自英特尔讨论在核的TSC的同步的另一个参考,在这种情况下,他们提到rdtscp可以读取两个TSC和处理器ID原子,这是在跟踪应用中很重要的事实......假设你想跟踪执行可能从一个核心迁移到另一个,如果你这样做在两个独立的指令(非原子),那么你没有把握其核心的线程在它读取时钟的时间线程。

http://software.intel.com/en-us/articles/intel-gpa-tip-cannot-sychronize-cpu-timestamps/

所有插座/封装在主板上收到两个外部公共信号:

- 重启

- 参考时钟

所有插座看到同时RESET时供电主板,所有的处理器包从外部晶体振荡器接收参考时钟信号,并在所述处理器的内部时钟被保持在相(尽管通常具有高的乘法器,像25X)与电路称为锁相环(PLL)的相位。 最近处理器将时钟在最高频率(乘数),该处理器被评为(所谓的恒定TSC)的TSC,无论乘法器任何单独芯可以是使用由于温度或电源管理节流的(所谓的不变TSC)。 像X5570 Nehalem处理器在2008年(和新的英特尔处理器)发布了支持“非停止TSC”,将继续在深度掉电C状态(C6)节电时滴答均匀。 请参阅此链接在不同的断电状态的详细信息:

http://www.anandtech.com/show/2199

在进一步的研究中,我遇到了一个专利申请英特尔在12/22/2009,并发表于2011/6/23题为“控制时间戳计数器(TSC)抵消了多张核心和线程”

http://www.freepatentsonline.com/y2011/0154090.html

谷歌的网页,以本专利申请(与链接USPTO页)

http://www.google.com/patents/US20110154090

从我收集有在非核一个TSC(在芯但并不排除任何核心的一部分周围的封装的逻辑),其在由VIPIN库马尔指定的机器特定寄存器的字段上的每个外部总线时钟递增由所述值在上面的链接(MSR_PLATFORM_INFO [15:8])。 外部总线时钟在133.33MHz运行。 此外,每个核心都有它自己的TSC寄存器,由被所有核心共享并且可从时钟的任何一个核心不同的时钟域主频 - 所以必须有某种缓冲当核心TSC由RDTSC读在一个核心上运行(或RDTSCP)指令。 例如,MSR_PLATFORM_INFO [15:8]可通过25设定为25上的包,每一个总线时钟非核TSC增量,存在由25乘以总线时钟,并且提供该时钟到每个内核时钟的PLL当地TSC寄存器,从而使所有TSC寄存器同步。 所以映射的术语,以实际硬件

- 恒定TSC是通过使用在133.33兆赫,这是通过在MSR_PLATFORM_INFO指定的恒定乘数运行外部总线时钟实现[15:8]

- 不变TSC通过保持在TSC每个核上的单独时钟域实现

- [:8 15]蜱在每个总线时钟,这样的多芯封装可以进入深度低功耗(C6状态),并且可以关闭PLL不停TSC是由具有由MSR_PLATFORM_INFO递增非核TSC来实现。 ..没有必要保持一个时钟在较高的乘数。 当核心从C6状态恢复内部TSC将得到初始化为非核TSC(就是那个没有去睡觉)的值与软件的情况下偏移调整写一个值到TSC,详情这是在该专利。 如果软件并写入到TSC则该核心的TSC将出与其他核相,但以恒定的偏移量(TSC时钟的频率都通过一个常数乘法器绑在总线参考时钟)。

RTDSC是不是在CPU同步。 因此,你不能在多处理器系统依赖于它。 我能想到的Linux的唯一的解决方法是实际限制由设置在单个CPU上运行其亲和力的过程。 这可以使用在外部使用来完成taskset实用程序或“内部的”使用了sched_setaffinity或pthread_setaffinity_np功能。

这本手册 ,章节17.12,介绍了最新的处理器使用的不变TSC。 可用的Nehalem这个时间戳,与rtscp指令一起,允许一个读时间戳(不受等待状态,等),并在一个原子操作的处理器签名。

它被认为是适合于计算挂钟时间,但它显然并不期待值是相同的处理器之间。 所陈述的想法是,你可以对同一个CPU的时钟看是否连续读取,或调整到多个CPU读取。 “它也可以被用来调节用于在NUMA系统在TSC值每个CPU的差异”。

另见多个CPU内核RDTSC精度

但是,我不知道的是,在接受的答案最终一致性的结论不同于TSC可用于挂钟时间的声明如下。 如果是一致的,是什么原因会有的原子确定的时间CPU源。

NB的TSC信息已经从第11章中,英特尔手册第17章。

文章来源: CPU TSC fetch operation especially in multicore-multi-processor environment