我想乘到整数,修改部分如下

( 由幂级数求和与负术语乘法 )

我做了什么,找到分数转换为CSD格式的方法。 但我想知道我怎么可以申请繁衍整数。

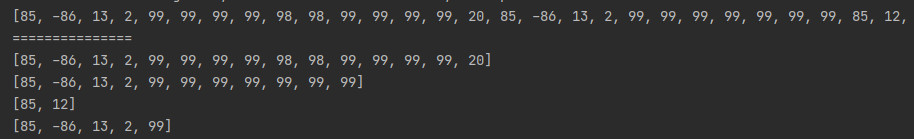

例如,我得到这个

0.46194 = 2 ^ -1 - 2 ^ -5 - 2 ^ -7 + 2 ^ -10。

然后我就可以得到这样的Verilog的RTL表达式:

Y =(X >> 1) - (X >> 5) - (X >> 7)+(X >> 10);

但问题是,如果我得到了什么输入值为3,那我怎么才能计算出上面的代码?

Y =(3 >> 1) - (3 >> 5) - (3 >> 7)+(3 >> 10);

但据我所知,这的确是不可能的计算。 因为3 >> 1为1,(3 >> 5)为0,(3 >> 7)为0,(3 >> 10)为0;

所以我不能得到正常的结果。 也发现修改后的分数表达的原因已经消失。 然后这个帖子的问题点是“我怎么能修改分数适用于整数”。

UPDATE:这应该是这样的。 Y =((3 << 1024)>> 1) - ((3 << 1024)>> 5) - ((3 << 1024)>> 7)+((3 << 1024)>> 10);

如果我们有reg [3:0]我们可以认为它可以容纳整数值0〜15。

现在,我们希望有分数的信息,我们必须感知加小数位,但到VERILOG的数量仍是一个整数。

我们仍然有4位,但我们改变二进制加权,而不是8 4 2 1到2 1 0.5 0.25 。 但Verilog的不知道这是所有关于我们如何解释的位模式。

在问题的右边>>只是代表小数位。 也使用T来表示-1在CSD术语

2^-1 - 2^-5 - 2^-7 + 2^-10.

Decimal 0.5 - 0.03125 - 0.0078125 + 0.0009765625

Binary 0.1000T0T001

正如你所指出的移位数将导致截断为整数。 关键是在这之前,小数位添加到数。

例如至10把个小数位添加到传入的整数:

input [9:0] a,

wire [19:0] a_frac = { a, 10'b0};

记住的Verilog认为这是一个整数,但我们必须有不同的解释的数量。

wire [19:0] y = (a_frac>>1) - (a_frac>>5) - (a_frac>>7) + (a_frac>>10);

y现在应该包含的东西,当你离开房间的移值。 输出将具有10个整数位和10位小数位。

要显示的号码,你可以扩展一个真实的:

$display("%d * 0.46194 = %f", a, y * 2.0**-10);

注:我会避免x作为变量的Verilog作为x采用了Verilog HDL有特殊的意义,要么不关心或在电线未知的值。

在EDA游乐场一个简单的例子 。