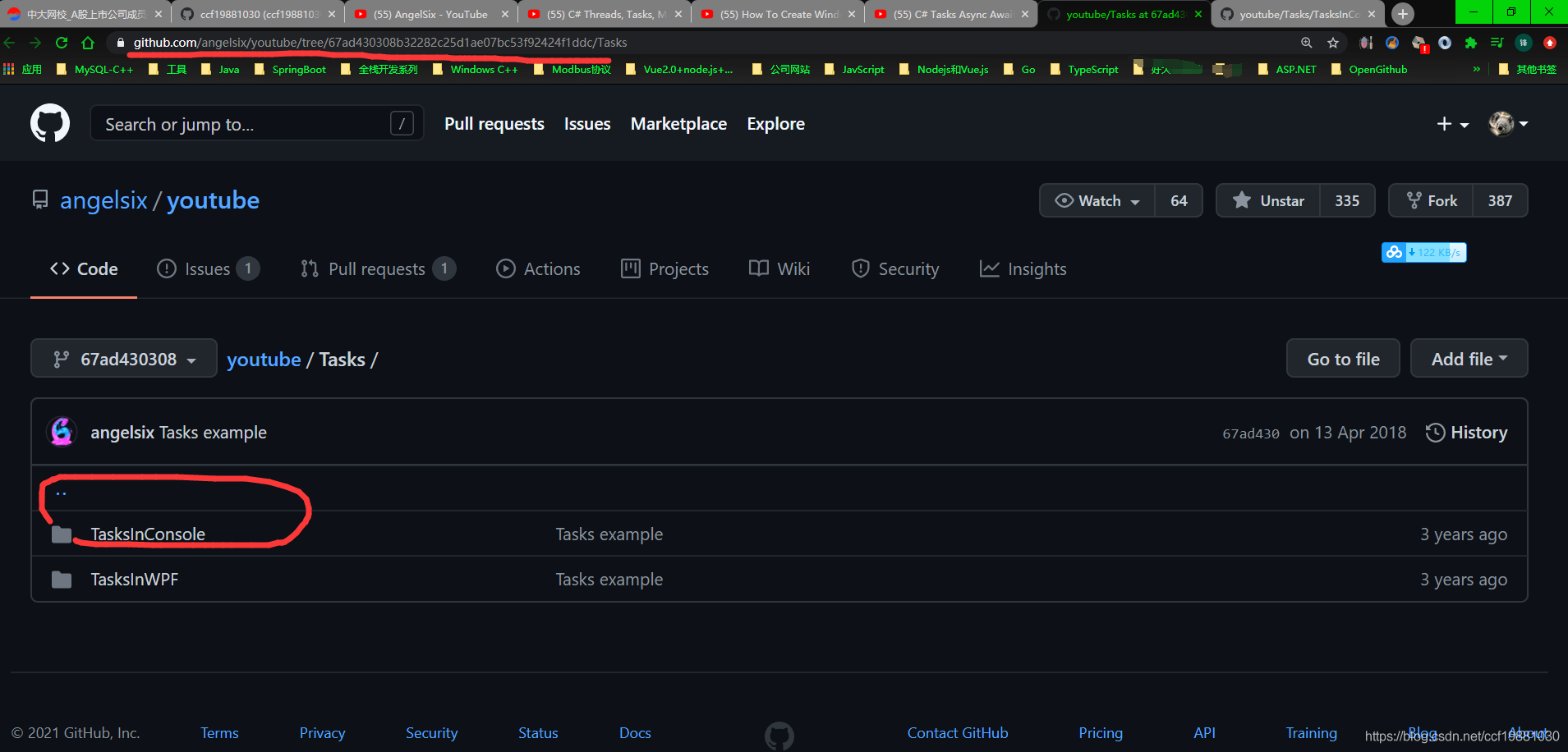

I posted this digital logic diagram as an answer to another stackoverflow question. It describes a logic system which will be coded in Verilog or VHDL and eventually implemented in an FPGA.

alt text http://img145.imageshack.us/img145/5125/bitshifterlogicdiagramkn7.jpg

The numbered boxes in the diagram represent bits in a field. Each field has K bits, and the bits for current and mask will be provided by a computer system (using a latched register or equivalent). The bits in next will be read back into that same computer system.

The solution that I posted works as long as there is at least one bit set in the mask field, and there is exactly one bit set in the current bit field. The idea is that the next bit field will become the current bit field after the computer system has performed some task (a scheduling operation, in the original question).

So, my question is this: How would you modify this system so that it properly handles the special case where the current bit field is all zero (no bits set)? As it stands, if all bits in current are zero, the output will also be zero, no matter what the bits in mask are set to.

Ideally, if current is all zeroes, the lowest set bit in mask should be set in next. The system should also still remain scalable to any number of bits (K) without having to add exponentially more logic gates. The spirit of the original question was to come up with a solution that would be straightforward to implement for any number of bits.

See also: this stackoverflow question