When MCR or MRC instructions execute with different cRm or opt2, then what is the status of cRn register?

For example if run:

asm volatile("mcr p15, 0, %0, c9, c13, 0" : : "r"(val))

or

asm volatile("mcr p15, 0, %0, c9, c13, 2" : : "r"(val))

then, which register's value will be changed c9 or c13? and what is the role of last option(0 or 2)?.here

The MCR and MRC instructions are generic coprocessor instructions. What these instructions do depends on the particular hardware you're using, what coprocessors it has, and the values of the opcode and coprocessor register operands (opcode1, opcode2, CRn and CRm). The coprocessor register operands don't necessarily refer to actual coprocessor registers, and so are effectively additional opcode operands.

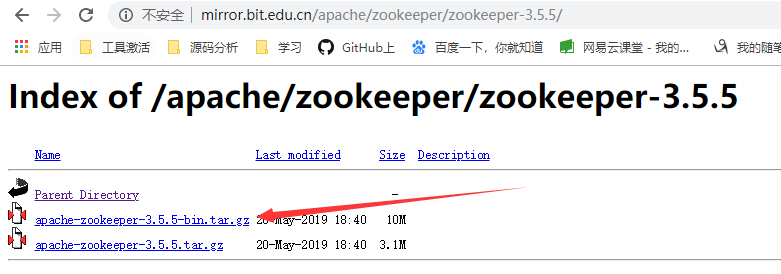

To find out what an MCR/MRC nstructions does, you need to look up it up in the hardware specific documentation the particular CPU this code is meant to run under. So with your examples we need to look in the Cortex-A7's documentation for coprocessor 15, which is the System Control "coprocessor". This page lists the System Control registers that can be accessed using these instructions in CRn, opcode1, CRm, opcode2 order.

In both your examples CRn is c9, and looking that up in the documentation leads to us to a page describing mostly performance monitoring related registers. In your first example opcode1 is 0, CRm is 13, and opcode2 is 0, which this page tells us that the instruction writes to the PMCR or Performance Monitor Control Register. With the second example opcode1 is 0, CRm is 13, and opcode2 is 2, meaning it accesses the PMNCNTENCLR or Count Enable Clear Register.

You're better off thinking that op1, op2, crn and crm form a certain register address. The latter instruction sets the co-processor 15 register 0, c9, c13, 2 (PMXEVCNTR, Performance Monitors Event Count Register) to the value contained in the register the C compiler decides to use for variable 'val'.

For other than performance counter registers:

B3.17.1 CP15 register summary by coprocessor register number

Figure B3-26 summarizes the grouping of CP15 registers by primary coprocessor register number for a VMSAv7

implementation.

CRn opc1 CRm opc2

c0 {0-2} {c0-c7} {0-7} ¶ ID registers

c1 {0, 4} {c0, c1} {0-7} System control registers

c2 {0, 4} {c0, c1} {0-2} Memory protection and

c3 0 c0 0 control registers

c5 {0, 4} {c0,c1} {0,1} Memory system

c6 {0, 4} c0 {0, 2, 4} fault registers

c7 {0, 4} Various Various ¶ Cache maintenance, address translations, miscellaneous

c8 {0, 4} Various Various TLB maintenance operations

c9 {0-7} Various {0-7} ¶ Reserved for performance monitors and maintenance operations

c10 {0-7} Various {0-7} ¶ Memory mapping registers and TLB operations

c11 {0-7} {c0-c8,c15} {0-7} ¶ Reserved for DMA operations for TCM access

c12 {0, 4} {c0,c1} {0,1} ¶ Security Extensions registers, if implemented

c13 {0, 4} c0 {0-4} ¶ Process, context, and thread ID registers

c14 {0-7} {c0-c15} {0-7} ¶ Generic Timer registers, if implemented

c15 {0-7} {c0-c15} {0-7} ¶ IMPLEMENTATION DEFINED registers

Read-only Read/Write Write-only ¶ Access depends on the implementation

Figure B3-26 CP15 register grouping by primary coprocessor register, CRn, VMSA implementation

About debug registers, there is a description:

C6.4.1 Using CP14 to access debug registers

Accesses to registers that are visible in the CP14 interface generally use the following coprocessor instructions:

• MRC for read accesses.

• MCR for write accesses.

In addition, the following coprocessors instructions are defined for specific registers accesses:

MRRC Read access to the Debug ROM Address Register, DBGDRAR, and the Debug Self Address Offset

Register, DBGDSAR, in an implementation that includes the Large Physical Address Extension.

STC Read access to the Host to Target Data Transfer Register, DBGDTRRXint.

LDC Write access to the Target to Host Data Transfer Register, DBGDTRTXint.

Form of MRC and MCR instructions

The form of the MRC and MCR instructions used for accessing debug registers through the CP14 interface is:

MRC p14, 0, <Rt>, <CRn>, <CRm>, <opc2> ; Read

MCR p14, 0, <Rt>, <CRn>, <CRm>, <opc2> ; Write

Where <Rt> refers to any of the ARM core registers R0-R14. Use of R13 is UNPREDICTABLE in Thumb and

ThumbEE states, and is deprecated in ARM state. <CRn>, <CRm>, and <opc2> are mapped from the debug register

number as shown in Figure C6-1

The use of the MRC APSR_nzcv form of the MRC instruction is permitted for reads of the DBGDSCRint only. Use with

other registers is UNPREDICTABLE. See CP14 interface 32-bit access instructions, required in all versions of the

Debug architecture on page C6-2124 for more information.

For accesses to the debug registers, <CRn> <= 0b0111 and therefore bit[10] of the value in the figure is 0.

10 9 8 7 6 5 4 3 2 1 0

Value 0 Register number[9:0]

Arguments CRn[3:0] opc2[2:0] CRm[3:0]

Figure C6-1 Mapping from debug register number to CP14 instruction arguments