I need to write optimized NEON code for a project and I'm perfectly happy to write assembly language, but for portability/maintainability I'm using NEON instrinsics. This code needs to be as fast as possible, so I'm using my experience in ARM optimization to properly interleave instructions and avoid pipe stalls. No matter what I do, GCC works against me and creates slower code full of stalls.

Does anyone know how to have GCC get out of the way and just translate my intrinsics into code?

Here's an example: I have a simple loop which negates and copies floating point values. It works with 4 sets of 4 at a time to allow some time for the memory to load and instructions to execute. There are plenty of registers left over, so it's got no reason to mangle things so badly.

float32x4_t f32_0, f32_1, f32_2, f32_3;

int x;

for (x=0; x<n-15; x+=16)

{

f32_0 = vld1q_f32(&s[x]);

f32_1 = vld1q_f32(&s[x+4]);

f32_2 = vld1q_f32(&s[x+8]);

f32_3 = vld1q_f32(&s[x+12]);

__builtin_prefetch(&s[x+64]);

f32_0 = vnegq_f32(f32_0);

f32_1 = vnegq_f32(f32_1);

f32_2 = vnegq_f32(f32_2);

f32_3 = vnegq_f32(f32_3);

vst1q_f32(&d[x], f32_0);

vst1q_f32(&d[x+4], f32_1);

vst1q_f32(&d[x+8], f32_2);

vst1q_f32(&d[x+12], f32_3);

}

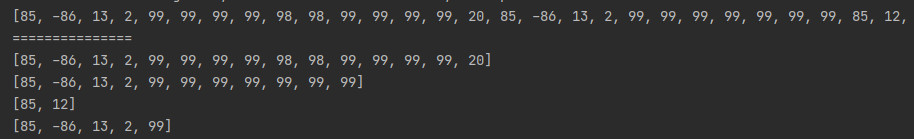

This is the code it generates:

vld1.32 {d18-d19}, [r5]

vneg.f32 q9,q9 <-- GCC intentionally causes stalls

add r7,r7,#16

vld1.32 {d22-d23}, [r8]

add r5,r1,r4

vneg.f32 q11,q11 <-- all of my interleaving is undone (why?!!?)

add r8,r3,#256

vld1.32 {d20-d21}, [r10]

add r4,r1,r3

vneg.f32 q10,q10

add lr,r1,lr

vld1.32 {d16-d17}, [r9]

add ip,r1,ip

vneg.f32 q8,q8

More info:

- GCC 4.9.2 for Raspbian

- compiler flags:

-c -fPIE -march=armv7-a -Wall -O3 -mfloat-abi=hard -mfpu=neon

When I write the loop in ASM code patterned exactly as my intrinsics (without even making use of extra src/dest registers to gain some free ARM cycles), it's still faster than GCC's code.

Update: I appreciate James' answer, but in the scheme of things, it doesn't really help with the problem. The simplest of my functions perform a little better with the cortex-a7 option, but the majority saw no change. The sad truth is that GCC's optimization of intrinsics is not great. When I worked with the Microsoft ARM compiler a few years ago, it consistently created well crafted output for NEON intrinsics while GCC consistently stumbled. With GCC 4.9.x, nothing has changed. I certainly appreciate the FOSS nature of GCC and the greater GNU effort, but there is no denying that it doesn't do as good a job as Intel, Microsoft or even ARM's compilers.