我目前正在写一个应该支持AXI4精简版(AXI4L),以及一个主AXI4。

我的主人AXI4从16位接口接收数据。 这是对赛灵思Spartan 6 FPGA和我打算使用EDK AXI4互连IP,它具有32位的最小宽度WDATA。

起初,我想用窄突发,即AWSIZE = X“01”(在传输2个字节)。 然而,我发现,Xilinx公司AXI参考指南UG761指出,‘窄脉冲[是]支持,但[...]不推荐。’ 未对齐的交易都应该得到支持。

这迫使我思考。 说我开始不对齐爆:

- AWLEN = X “01”(2次)

- AWSIZE = X “02”(在转移“4个字节)

并执行以下操作:

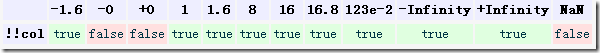

AX (32-bit word #0: send hi16)

XB (32-bit word #1: send lo16)

其中A,B是我,在未对齐的(2字节对齐的)地址开始的16位字。 X表示WSTRB被取消断言针对所指示的16位。

- 这是支持或执行此落入类别“窄脉冲串”甚至通过AWSIZE = X“02”(在传输4个字节),而不是下AWSIZE = X“01”(2个字节中传递)?

现在,如果这只是为了AXI4,我可能不会因为AXI4外设都需要使用WSTRB信号关心我这个用例。 然而,AXI参考指南UG761规定“[AXI4L]从站接口可以选择忽略WSTRB(假设所有字节有效)。”

我读到这里 ,很多(但不是全部;并没有列出?)赛灵思AXI4L外设都选择忽略WSTRB。

- 这是否意味着我基本上是从做窄突发(“不建议”),以及未对齐的突发(“WSTRB可以忽略不计”)或禁止有一个简单的办法卸载一些实施工作从我掌握到的互连, 确保访问AXI4L外围设备后,系统的正常行为?

你举的例子不是一个狭窄的破灭,应该工作。

不推荐窄爆裂的原因是,它给了次优的性能。 两个窄脉冲串和在区域数据realignement成本,因此不推荐IMHO。 然而,DRE具有最小的带宽成本,同时窄爆一样。 如果您的AXI端口为100MHz的32位,则有3.2GBits最大吞吐量,如果使用16位的50%的时间窄突发,比你的最大吞吐量减小到2.4GBits(32位X 50MHz的16位+ X 50MHZ)。 另外,我不知道AXI-精简版支持窄脉冲或数据realignement。

你举的例子有两个主要的缺陷。 首先,它要求3的数据节拍传送32位,这是比窄突发最差(I不认为AXI足够聪明取消与WSTRB最后脉冲串0)。 其次,你可以不爆在同一时间超过2个16位,如果你有大量的数据传输,这将挂起您的AXI基础设施的性能。

对付这种情况的最好办法是在16位串联在一起,形成在块32位。 然后你缓冲这些32位和突发他们,当你有足够的。 这是AXI高性能的方式来做到这一点。

但是,如果收到的数据为16位,看来你会使用AXI-Stream的支持16位,但没有地址的概念更好。 您可以采用Xilinx公司的IP核的AXI-流映射到AXI-4。 无论是AXI-数据移动或AXI-DMA可以做到这一点。 都做同样的(事实上,AXI-DMA包括数据移动),但AXI-DMA控制槽的AXI-精简版接口而DATAMOVER通过additionals AXI流控制。

最后一点,赛灵思内核从来没有要求窄脉冲串或DRE。 如果您在AXI-DMA需要DRE,它是由AXI-DMA的核心,而不是AXI互连完成。 此外,这些核心是明确的来源,所以你可以检出他们很容易是如何运作的。

文章来源: AXI4 (Lite) Narrow Burst vs. Unaligned Burst Clarification/Compatibility