I am new to verilog. I am writing the code for a 10x16 Round-Shift register. Can you help me with the error and also if any optimizations can be done?

module shift_reg_v(

output [15:0] word_out

);

integer i;

integer j;

reg [159:0] coeff;

reg [15:0] word;

initial

begin

for (i=0;i<160;i=i+1)

begin

coeff[i] = 0;

end

for (i=0;i<16;i=i+1)

begin

word[i] = 0;

end

end

always

begin

for (j=0;j < 10;j = j+1)

begin

for (i=0;i < 16;i = i+1)

begin

if (j==0)

begin

word[i] = coeff[(16*(j+1))+i];

end

else

begin

coeff[(16*j)+i] = coeff[(16*(j+1))+i];

end

end

end

coeff[159:144] = word[15:0];

word_out[15:0] = word[15:0];

end

endmodule

The program is showing 2 errors at the output line:

word_out[15:0] = word[15:0];

Referring to error:

Error-[IBLHS-NONREG] Illegal behavioral left hand side

a.sv, 42

Non reg type is not valid on the left hand side of this assignment

The offending expression is : word_out[15:0]

Source info: word_out[15:0] = word[15:0];

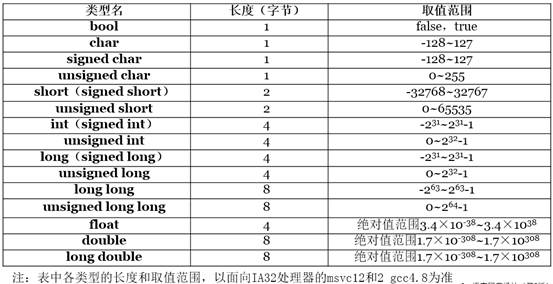

The LHS of any procedural assignment statement must be of reg type. Procedural assignment statements assign values to reg, integer, real, or time variables and can not assign values to wire. Note that reg can hold or store some value depending on some triggering event, while wire cannot store any value.

Make word_out as reg as follows:

module shift_reg_v(

output reg [15:0] word_out

);

Referring to the warning:

Warning-[PALF] Potential always loop found

a.sv, 24

This always block has no event control or delay statements, it might

cause an infinite loop in simulation.

Moreover, you have not given any sensitivity for always block execution. This might result in infinite loop. There is no triggering control for always block. Henceforth the block shall execute infinitely.

Use always @(*) (or always_comb in SystemVerilog) for automatic sensitivity list in combinational logic.

As a side note, you might have a clk, as clocking input to the module and make the always block work on the edge of clock. This will help in modelling sequential logic. (Note the usage of nonblocking assignments <= in case of sequential logic).

Refer this PDF for difference between reg and nets.Also, this always block might be useful.

Also, you need to correct following code :-

coeff[i] = 0;

It is a bit assignment and should clearly specify that as coding practice.

coeff[i] = 'h0;