我试图合成自己编写的VHDL模块。

代码如下:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

use IEEE.NUMERIC_STD.ALL;

entity ClockCounter is

port(

clk : in std_logic;

input : in std_logic;

enable : in std_logic;

output : out std_logic := '0';

bitReady : out std_logic := '0';

countError : out std_logic := '0'

);

end ClockCounter;

architecture Behavioral of ClockCounter is

signal totalBitWidth : integer := 4;

signal majorityValue : integer := 3;

begin

totalBitWidth <= 4;

majorityValue <= 3;

-- Process for recognizing a single input value from a clock cycle

-- wide input signal

majority_proc: process(clk, input, enable)

variable clkCount : integer := 0;

variable Sum : integer := 0;

begin

if rising_edge(clk) And enable = '1' then

-- Reset bitReady after one clock cycle

bitReady <= '0';

-- Check the input value and add it to the Sum variable

if input = '1' then

Sum := Sum + 1;

else

Sum := Sum + 0;

end if;

-- Increment the clock counter variable

clkCount := clkCount + 1;

-- Check if the clock count has reached the specified number of cycles

if clkCount >= totalBitWidth then

-- Determine if the Sum variable has met the threshold for

-- value of 1, set the output accordingly

if Sum >= majorityValue then

output <= '1';

else

output <= '0';

end if;

-- This checks if the value for all clock cycles was the same and

-- sets an error flag if not

if Sum = totalBitWidth Or Sum = 0 then

countError <= '0';

else

countError <= '1';

end if;

-- Reset the clock counter and sum value

clkCount := 0;

Sum := 0;

-- Set the bit counter high to alert other midules that a new bit

-- has been received

bitReady <= '1';

end if;

elsif enable = '0' then

clkCount := 0;

Sum := 0;

end if;

end process;

end Behavioral;

我得到的问题是这样的尝试合成时:

警告:XST:1293 - FF /锁存器具有0在块的恒定值。 这FF /锁存器将在优化过程中进行修整。 警告:XST:1896 - 由于其它FF /锁存修整,FF /闩锁具有0在块的恒定值。 这FF /锁存器将在优化过程中进行修整。 警告:XST:1896 - 由于其它FF /锁存修整,FF /闩锁具有0在块的恒定值。 这FF /锁存器将在优化过程中进行修整。

修整去一路下跌到。

我不明白的是,clkCount变量是最多增加高达6的整数,然后重置为0。

难道这些警告的东西我可以忽略?

该模块是分开更大的系统的我的工作,当我合成更大的系统我得到了很多的

结果1位锁存器信号

所以,我试图做的是固定的上层模块之前消除低级模块尽可能多的警告越好。

任何帮助将是巨大的。 谢谢

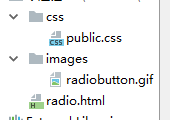

PS - 我使用赛灵思Spartan 6 SP605评估套件板,并在Project Navigator。