I'm a beginner to vhdl. I am trying to write a VHDL code to describe the behavior of a traffic light. It has 3 signal outputs Yellow (0), Green (1) and Red (2). Initially the light is yellow. It would be turning to Green after 10ns. Green would turn to red after 40ns and red would come back to yellow after 60ns. The state machine is not having any external input and is a free running machine synchronized by a 10ns clock (total time period = 10ns). Traffic light has an external reset control signal to reset the light to yellow.I need to show the testbench with 2 times reset cases and free running output signals in unsigned decimal format.

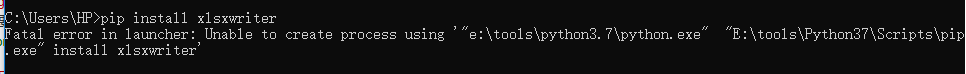

The vhdl code runs fine on Forcing clock and by removing the code for rst_process in testbench but the rst_process of test-bench doesn't work as expected(goes undefined in simulation)

This is the main vhdl code

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity traf is

Port ( clk : in STD_LOGIC;

rst : in STD_LOGIC;

Green : out STD_LOGIC;

Red : out STD_LOGIC;

Yellow : out STD_LOGIC);

end traf;

architecture Behavioral of traf is

signal count:integer range 0 to 10 := 0;

signal state:integer range 0 to 2 := 0;

begin

process(clk, rst)

begin

if(rst = '1') then

state <= 0;

Red <= '0';

Green <= '0';

Yellow <= '1';

count <= 0;

elsif clk'event and clk='1' then

case state is

when 0 => --Yellow Light

if(count=1) then

count <= 0;

state <= 1;

else

count <= (count + 1);

Red <= '0';

Green <= '0';

Yellow <= '1';

end if;

when 1 => --Green Light

if(count=4) then

count <= 0;

state <= 2;

else

count <= count + 1;

Red <= '0';

Green <= '1';

Yellow <= '0';

end if;

when 2 => --Red Light

if(count=6) then

count <= 0;

state <= 0;

else

count <= count + 1;

Red <= '1';

Green <= '0';

Yellow <= '0';

end if;

when others =>

state <= 0;

count <= 0;

end case;

end if;

end process;

end Behavioral;

This is the testbench code

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity tb is

-- Port ( );

end tb;

architecture Behavioral of tb is

signal clk,rst,Green,Red,Yellow:std_logic;

constant clk_period : time:=10 ns;

component traf is

Port (

clk : in STD_LOGIC;

rst : in STD_LOGIC;

Green : out STD_LOGIC;

Red : out STD_LOGIC;

Yellow : out STD_LOGIC

);

end component;

begin

DUT:traf PORT MAP

(

clk=>clk,

rst=>rst,

Green=>Green,

Red=>Red,

Yellow=>Yellow

);

clk_process:process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

rst_process:process

begin

rst <= '0';

wait for clk_period * 15;

rst <= '1';

wait for clk_period;

rst <= '0';

wait for clk_period * 50;

rst <= '1';

wait for clk_period*2;

rst <= '0';

wait;

end proocess;

end Behavioral;