I want to get an accurate power report that contains real dynamic and static power consumption. I'm working on Xilinx spartan3 board. My code has no errors but after selecting the "Generate Text Power Report" in ISE (Xilinx synthesis tool), always the power report shows that my design has no dynamic power consumption. (Why?)

Power report :

Dynamic = 0.00

Quiescent = 59.84

Total = 59.84

My code :

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY SRAM IS

PORT(

clk : IN std_logic;

wr : IN std_logic;

din : IN std_logic_vector(7 DOWNTO 0);

dout : OUT std_logic_vector(7 DOWNTO 0);

addr : IN INTEGER RANGE 0 TO 3

);

END SRAM;

ARCHITECTURE Behavioral OF SRAM IS

TYPE matrix IS ARRAY (0 TO 3) OF std_logic_vector(7 DOWNTO 0);

SIGNAL mem : matrix;

BEGIN

PROCESS(clk)

BEGIN

IF clk = '1' AND clk'event THEN

IF wr = '1' THEN

mem(addr) <= din;

END IF;

END IF;

END PROCESS;

dout <= mem(addr);

END Behavioral;

list of warnings :

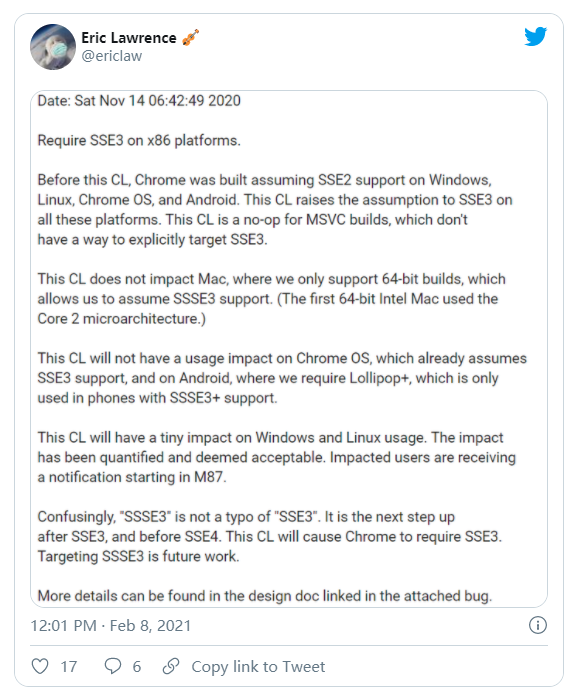

Design load 20% completeDesign load 25% completeDesign load 30% completeDesign load 60% completeDesign load 95% completeDesign load 100% completeWARNING:PowerEstimator:270 - Power estimate is considered inaccurate. To see

WARNING:Power:1337 - Clock frequency for clock net "clk_BUFGP" is zero.

WARNING:Power:1337 - Clock frequency for clock net "clk_BUFGP/IBUFG" is zero.

WARNING:Power:1369 - Clock frequency for one or more clocks was not found

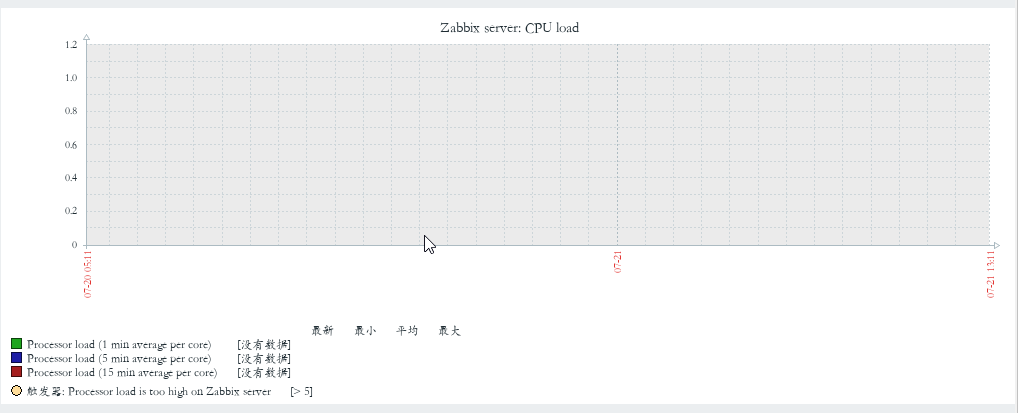

According to the "Brian" comment I edit the result of power report :

Clocks = 0.92 mw

Logic = 0.00 mw

Signals = 0.09 mw

IOs = 0.15 mw

Quiescent = 59.85 mw

Total = 61.01 mw