I want to detect a rising edge of a signal from a flip-flop AA to BB

+----+

A ----------------| |----- OUT

+----+ | BB |

B ----| |------|> |

| AA | +----+

clk ----|> |

+----+

Verilog code:

module edge_detect (

input A,

input B,

input clk,

output OUT

);

reg AA;

reg BB;

always @(posedge clk) begin

AA <= B;

end

always @(posedge AA)begin

BB <= A;

end

assign OUT = BB;

endmodule

The output of AA is used as a clock to BB saying that AA has done its job and then BB can now continue its operation.

I rarely see this code. Is this a good practice?

If not, are there any other proper way to detect an edge of a signal?

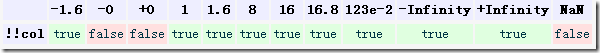

People tend to frown on using data as clocks for various reason.

Personally if I was writing this I'd go with:

module edge_detect (

input A,

input B,

input clk,

output OUT

);

reg AA;

reg BB;

wire enA;

always @(posedge clk) begin

BB <= B;

end

assign enA = !BB && B;

always @(posedge clk)begin

if (enA) begin

AA <= A;

end

end

assign OUT = AA;

endmodule

+----+

A ----------------------------|D |----- OUT

+---+ | AA |

/--------------| | | |

| +----+ |AND|------|E |

B ----| |------o| | | |

| BB | +---+ | |

clk ----|> | clk ----|> |

+----+ +----+

The behaviour is a little different though.

If you wanna detect a rising or a falling edge in Verilog, simply pipeline or delay the signal by 1 clock pulse. In a digital environment, an edge can be thought of as a 0 to 1 transition or 1 to 0 transition.

So you can check if the signal made a transition to either state and then assert your output high only for that condition.

For example :

output out_flag;

reg temp;

reg temp_d;

always@(posedge clk)

temp_d <= temp;

always@(posedge clk)

begin

if (temp && ~temp_d)

out_flag<= 1'b1;

else

out_flag<= 1'b0;

end