-This code is written in verilog using Modelsim 10.2d.The errors below indicate there is some problem with {cout,l3} assignment.

module alu(a,b,bin,cin,op,cout,res);

input [31:0] a,b;

input [1:0] op;

input bin,cin;

reg [31:0] l1,l2,l3;

output cout;

output [31:0] res;

assign l1 = a & b;

assign l2 = a | b;

initial

if(bin == 1'b0)

assign {cout,l3} = a + b + cin;

else

assign {cout,l3} = a - b + cin;

mux4to1(l1,l2,l3,op,res);

endmodule

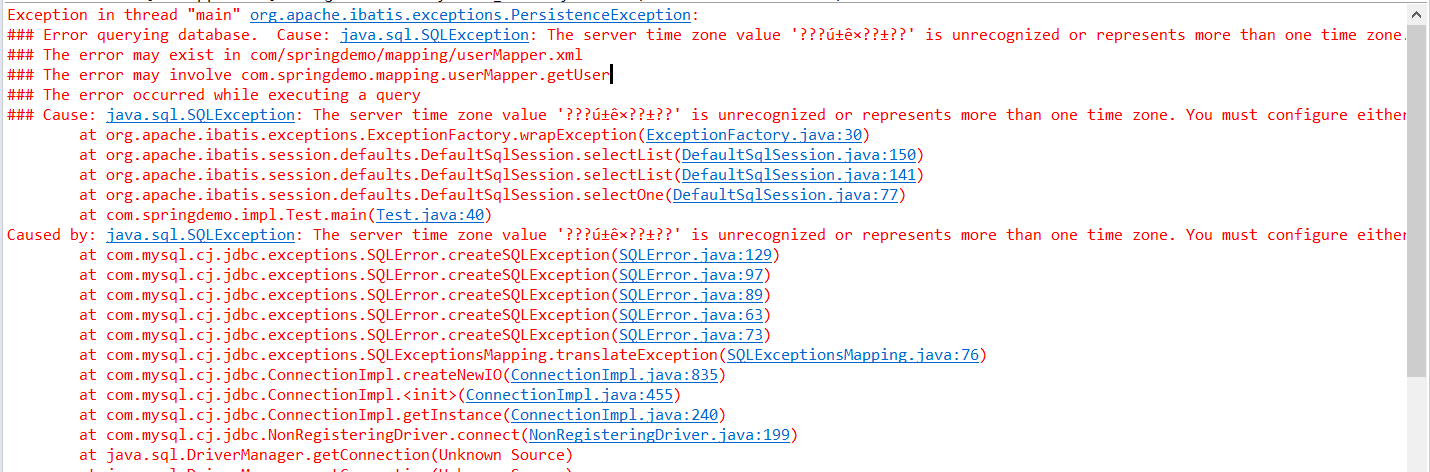

Error-

v(14): LHS in procedural continuous assignment may not be a net: cout.

v(16): LHS in procedural continuous assignment may not be a net: cout.

wire can not be assigned inside an initial or always block. You should change the type to reg.

The initial block will only be run once at the start of the simulation, not continually evaluated, therefore you should use always instead.

//...

output reg cout;

//...

always @* begin

if(bin == 1'b0) begin

{cout,l3} = a + b + cin;

end

else begin

{cout,l3} = a - b + cin;

end

end

There will be a few more issues in your code.

1.

assign l1 = a & b;

assign l2 = a | b;

The primary rule with continuous assignments is that the LHS must be a net. The reason for this rule is that registers get values at discrete times, but nets are always driven by a value. Changes to a net may happen asynchronously.

2.Errors in your code

You can assign values inside an always block(Quasi continuous assign), but the LHS must be a register.This is an advanced feature in verilog,I strongly recommend that you dont use it.FOr simplicity, do not use assign in an always block and all the assignments in the block should be registers(i.e Lhs)

CHANGES TO YOUR CODE

wire[31:0] l1,l2;

...

if(bin == 1'b0)

{cout,l3} = a + b + cin;

else

{cout,l3} = a - b + cin;