There is very little information how to configure the Beaglebone for PWM on newer versions of the kernel. I followed the instructions from PWM on BeagleBone Black (v4.14) to interface with the PWM chips, but now I need to figure out the pin that each chip is connected to.

Based on the Cape Expansion Headers image in the BeagleBone Black documentation, I know:

EHRPWM0A = P9_22EHRPWM0B = P9_21EHRPWM1A = P9_14EHRPWM1B = P9_16EHRPWM2A = P8_19EHRPWM2B = P8_13ECAP0 = P9_42

When I run ls -lh /sys/class/pwm to see the available PWM interfaces I see:

lrwxrwxrwx 1 root pwm 0 May 6 14:31 pwmchip0 -> ../../devices/platform/ocp/48300000.epwmss/48300100.ecap/pwm/pwmchip0

lrwxrwxrwx 1 root pwm 0 May 6 14:31 pwmchip1 -> ../../devices/platform/ocp/48300000.epwmss/48300200.pwm/pwm/pwmchip1

lrwxrwxrwx 1 root pwm 0 May 6 14:31 pwmchip3 -> ../../devices/platform/ocp/48302000.epwmss/48302200.pwm/pwm/pwmchip3

lrwxrwxrwx 1 root pwm 0 May 6 14:31 pwmchip5 -> ../../devices/platform/ocp/48304000.epwmss/48304100.ecap/pwm/pwmchip5

lrwxrwxrwx 1 root pwm 0 May 6 14:31 pwmchip6 -> ../../devices/platform/ocp/48304000.epwmss/48304200.pwm/pwm/pwmchip6

When I compare this to the BeagleBone PWM example, I see that the available chips and adresses are different. The example does mention that the PWMs can change, so I need to figure out the new mapping.

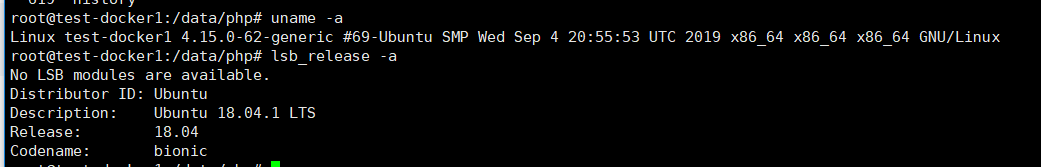

How do I determine the PWM chip to pin mapping? I am using a TI AM335x BeagleBone Black Wireless running kernel version 4.14.37-ti-r46.

Page 184 of the TI AM335x and AMIC110 Sitara Processors Technical Reference Manual gives the memory map for the PWM chips:

PWM Subsystem 0: 0x48300000

eCAP0: 0x48300100ePWM0: 0x48300200

PWM Subsystem 1: 0x48302000

eCAP1: 0x48302100ePWM1: 0x48302200

PWM Subsystem 2: 0x48304000

eCAP2: 0x48304100ePWM2: 0x48304180

The address of each PWM interface (posted in the question) contains the hardware address. Matching these addresses gives us:

EHRPWM0 (ePWM0) is pwmchip1EHRPWM1 (ePWM1) is pwmchip3EHRPWM2 (ePWM2) is pwmchip6ECAP0 (eCAP0) is pwmchip0

Each EHRPWM chip has two PWM output channels, thus the A and B variants. They are exported by echoing a 0 or 1 to export. These channels must use the same frequency, but can have a different duty cycle.

Therefore, given this interface configuration, EHRPWM0A and EHRPWM0B are located at:

root@beaglebone:~# cd /sys/class/pwm/pwmchip1

root@beaglebone:/sys/class/pwm/pwmchip1# ls

device export npwm power subsystem uevent unexport

To export EHRPWM0A (P9_22):

root@beaglebone:/sys/class/pwm/pwmchip0# echo 0 > export

root@beaglebone:/sys/class/pwm/pwmchip0# ls

device export npwm power pwm-1:0 subsystem uevent unexport

To export EHRPWM0B (P9_21):

root@beaglebone:/sys/class/pwm/pwmchip0# echo 1 > export

root@beaglebone:/sys/class/pwm/pwmchip0# ls

device export npwm power pwm-1:1 subsystem uevent unexport

Note: the list of available PWM interfaces and addresses may differ from the list provided in the question, but this method will still work to determine the final pin map.