I am quite new to Vivado and VHDL and I would like some guidance on a fundamental issue.

I am guessing that I can create my own libraries and use them in my projects as i do with the default and fundamental ones

eg:

library IEEE;

use IEEE.std_logic_1164.ALL;

use IEEE.std_logic_unsigned.ALL;

Now, by browsing on the net, I haven't found anything concrete as an answer, there is not any direct way to "add library" (at least in my version of Vivado).

Is there any way to build VHDL code with lets say type definitions and use them in any file you like, as it is done in C for example?

So libraries are just a method for dealing some name clashes. So Xilinx (or another vendor) can release a new entity and not have it clash with your existing objects. You can certainly do that as well, but it doesn't actually solve any problems for you.

Instead, what you are looking for is a package. Let's look at how we would use it:

Let's create another file tools.vhd

package tools is

type tribool is (true, false, maybe);

end package;

Which we could then use in our entities as:

use work.tools.all;

...

signal x : tribool := maybe;

Each file in VHDL resides inside a library (in Vivado, your designs file are in xil_defaultlib by default).

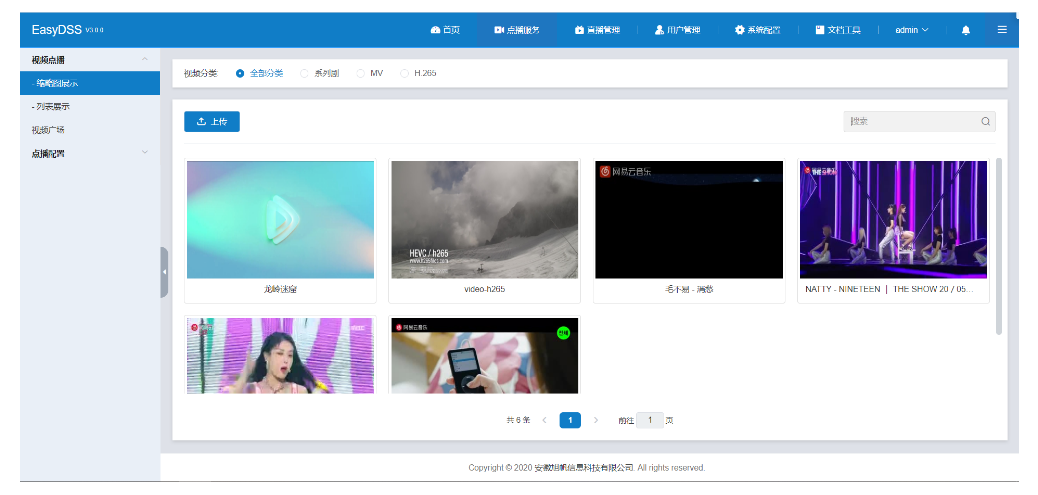

You can create/change the library a file resides in Vivado by clicking on the file, then clicking the button to the right of the Library label in the "Source File Properties" tab. You can create a library by assigning a file to a library that doesn't exist.

You will often see the library work in VHDL. Someone will correct me if I'm wrong, but work is not a library and only refers to the current library. Thus, if you have a package and an entity in the same library, you can refer the package as my_library.my_pkg or work.my_pkg.

If you want to handle libraries outside Vivado (for example large simulation models), you can precompile them, for example in Questa/Modelsim:

in vsim or .do file:

vlib path/to/MyLib

vmap MyLib path/to/MyLib

vcom -93 -work MyLib completely/other/path/to/MyLibSource.vhd

Now, Vivado has a tendency to overwrite the files in simulation folder, so don't put it there unless you want to re-compile it every time. However, Vivado should respect what is in modelsim.ini. So add to that:

MyLib = path/from/vivado/sim/to/Mylib

Now you can use MyLib as any other library:

library MyLib;

use MyLib.all;

. . .

i_MyAwesomeModel : entity MyLib.HalfAdder_Sim